Upgraded dielectric performance at the most fundamental level of ICs can have tremendous strategic leverage in memory and logic circuit development, today and tomorrow

Imagine being in a large room filled with people, each of whom has an important piece of information that you need. All of them will gladly tell you what they know, but there’s a problem: they’re all speaking at once. The more densely packed the room, the harder it is to distinguish the words of the person you’re trying to focus on from the surrounding cacophony.

The issue is crosstalk, defined by Wikipedia as “any phenomenon by which a signal transmitted on one circuit or channel of a transmission system creates an undesired effect in another circuit or channel.” And if you’re in the business of manufacturing memory and logic devices with billions of DRAM cells or logic transistors in extremely close proximity, you’re facing a situation a lot like that room full of talkative people.

Consider the typical DRAM cell: a capacitor, which holds a charge representing a 1 or 0; an access transistor; and a bitline, through which the capacitor’s charge is read. Over time, in the quest for greater density, speed and minimized power consumption, these structures have gotten smaller, and in recent years have evolved into 3D designs. In parallel, both the sensing voltage (∆V) and cell capacitance (Cs) have been reduced with each technology generation, thus necessitating a similar reduction in bitline capacitance (CBL).

In our roomful-of-people analogy, those reductions are the equivalent of the person you’re listening to speaking less distinctly, making it even more difficult to isolate their words. And similar dynamics are at work in the logic sector, where ever-greater parasitic capacitances (both between gates and between gates and gate contacts) have increased the risk of crosstalk.

Crosstalk has been with us since the earliest days of electronics, and fortunately there is a well-known way of addressing it: isolation. In our crowded room this might involve placing a sound baffle around each person; on an IC, it can often be accomplished with better dielectric films.

“Better” in this case doesn’t just mean a lower dielectric constant (k), although that’s an important factor. Films must also deposit without risk of damage to other circuit elements, and be able to survive subsequent thermal processing, etching, cleaning, and other steps without any change in their properties. They must be defect-free and uniform. And in this era of 3D circuit features, thickness uniformity is not enough — a film’s properties must also be uniform even when deposited in the vertical dimension.

There’s also an additional factor that comes into play: every advanced chipmaking organization faces intense competition and strives to develop its own unique methods for eking out a bit more yield here, a little more performance there. Engineers responsible for these process tweaks benefit from versatility and flexibility in the films they work with — the ability to tune a film’s composition to achieve different properties, including etch selectivity. Further, the higher density and complexity of each new technology generation makes these performance and yield gains more challenging to achieve. To revisit the roomful-of-people analogy, it’s as if the room gets ever-smaller, while the people talk louder. There’s less space for isolation but more need for it.

In the pre-3D era, process and integration engineers seeking isolation solutions could look to well-proven methods for deposition of tunable planar dielectrics or conformal SiO2 and nitrides. But today, there’s a need for both tunability and conformality, as well as the ability to deposit films containing Si-C bonds, such as silicon oxy-carbide (SiCO). These are required for greater etch selectivity, which is an increasingly important factor in many applications, from gate-all-around (GAA) spacers to BEOL dielectrics to advanced lithography processes. At the same time, there’s growing concern about plasma damage to circuit features.

So, what’s the way forward in the quest for isolation? One avenue is a new deposition technique, SPARC, that aligns well with these emerging needs. In addition to maintaining uniform composition and film properties throughout the depth of high-aspect-ratio features, SPARC enables deposition of highly conformal SiCO thin films, which provide effective isolation when used as low-k spacers in both logic and DRAM devices.

Within the SiCO family, the SPARC method enables wide composition tuning, while still maintaining excellent conformality. Dense, robust SiCO films with k of ~4-4.4 and low leakage can be deposited directly on metals such as Co, W, etc., without oxidizing the underlayer. The films show excellent adhesion while also being hermetic. Even at low deposition temperatures of 400°C, the carbon is fully cross-linked with very few or no terminal methyl groups, providing thermal and chemical stability compared to other SiOC films.

Importantly, all this is accomplished in a non-plasma environment. Ground-state radicals in the downstream interact only with specific bonds in carefully chosen precursor molecules. The choice of radical and precursor molecules makes bond-breaking selective, thereby creating precursor radicals that have very low sticking coefficients and consequently excellent step coverage. Si-C bonds are not broken during the deposition step, and any O, N, or C bound to silicon in the precursor molecule is retained. The design and choice of precursor are driven by the desired film type, to provide that wide composition tuning.

During this process, the ratio of Si-C bonds can be increased, with a reduction in Si-O bond density. Even with films deposited at different temperatures, the amount of cross-linked carbon is the primary driver for etch selectivity over density or total amount of carbon in the film. In addition, these SiCO films have zero wet etch rate (WER) in typical wet chemistries such as dilute HF and hot phosphoric acid, and thus offer near-infinite wet etch selectivity. The films are also continuous and pinhole-free down to at least 15Å, unlike ALD SiN films which need to be at least 30Å to be pinhole-free.

What does this look like in practice? Let’s go back to our DRAM cell example: as noted earlier, the continued node-to-node decline in cell capacitance has spurred a corresponding reduction in bitline capacitance to improve sensing (i.e., the ability to “hear the cell speak”).

A significant component (perhaps half) of bitline capacitance derives from coupling between the bitline and storage node cell (SNC). Since the 20nm node, the use of air gaps has been a means of reducing this coupling. Note the light-green lines on either side of the air gaps — these are dielectric films that must meet many stringent standards including conformality, adhesion, hermeticity, dielectric constant, and breakdown voltage. The characteristics of SPARC-deposited SiOC enable lower-capacitance coupling than traditional materials, and hence greater DRAM performance.

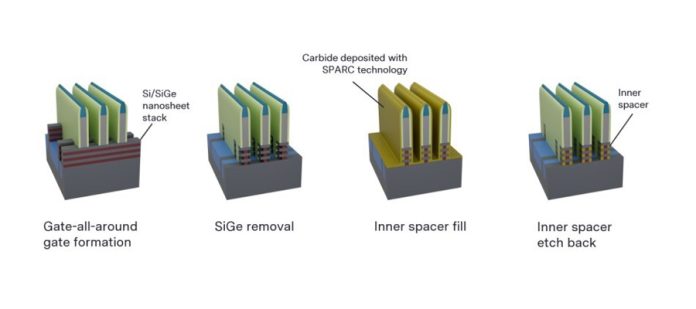

In logic, gate spacers have long been known as a means of reducing parasitic capacitances both between gates and between gates and gate contacts, thus reducing risk of crosstalk. The spacer concept has been carried over into 3D gate-all-around (GAA) architectures, but there’s an additional wrinkle: the spacer material must also serve as a lateral etch stop.

Again, the combination of characteristics exhibited by SPARC-deposited SiOC films is an excellent match for the situation. In addition to its electrical properties, SiOC’s high anisotropy and excellent etch selectivity offer improved fab-line performance over other options.

In both these examples, minimization of crosstalk is just one consideration among many. But it’s important to keep in mind that this minimization has great significance to the overall circuit development process, because it reduces the burden on the capacitor and transistor, making it easier for them to perform their desired functions. From a big-picture perspective, this means there’s less need to pursue other avenues towards improved performance, all of which necessarily come at a cost and can introduce new complications. It’s a great example of how a relatively subtle upgrade at a fundamental level can have tremendous leverage.

The high flexibility and adaptability of the SPARC process opens the door to a wide range of conformal films and compositions. For example, it can be used to deposit silicon carbon nitride (SiCN) films, again with a high level of tunability. High-quality conformal boron-based films, such as boron carbide (BC) and boron carbon nitride (BCN), have also been successfully deposited; they offer different sputtering and etch behavior than their Si-based counterparts.

One especially interesting potential application is for advanced patterning techniques, such as Self-Aligned Quadruple Patterning (SAQP), self-aligned gate and contact (SAGC), and fully self-aligned via (fSAV), that are being developed for production of increasingly complex 3D structures. All rely on materials with distinct etch selectivity to achieve new levels of overlay accuracy; they essentially require unique combinations of spacer, hardmask, and etch-stop materials, both planar and conformal, that exhibit near-perfect etch selectivity to one another in various plasma etch and wet chemistries. Films based on BC and BCN are good candidates because they also provide suitable k, conformality, electrical properties, and other characteristics.=

Likewise, SPARC-deposited films based on silicon carbide (Si-C) could prove very useful in 3D NAND memory hole fabrication as they offer good selectivity against oxides and nitrides, as well as tunability. And in any situation where plasma-based processing presents an issue, the ability to use radicals to create films of choice can put interesting new options into play.

Few industries evolve faster than semiconductor manufacturing, and that poses ongoing challenges for developing and integrating the ever-changing mix of production processes. As the industry continues to face new issues like 3D integration and enduring ones like crosstalk, it will require ingenuity and creativity to keep pace, and innovative tools like SPARC that support these efforts to ensure that each piece of information is heard clearly.