Introduction to signal compliance testing

It is nice to think of a PCB trace as simply the ideal route that a signal takes from a transmitter to a receiver and, at low data rates, this is a reasonable concept. At the data rates new-generation serial standards operate, additional physical phenomena are affecting signal integrity and need to be taken into account. All conductors in the signal path, including circuit board traces, vias, connectors and cabling, must be taken into account as transmission line effects can create return losses and reflections that degrade signal levels, introduce skew, and add noise.

Faster transition times, shorter unit intervals (UIs), impedance mismatches and noise sources in the frequency domain, contribute more to bit error rates which means a required change in one’s view of “digital” design. Engineers need to take a fresh look at their strategies for connectivity, pattern generation, receiver-side testing, data acquisition, and analysis. Coupling these issues with evolving new standards and tighter compliance testing requirements creates a tougher job for companies to quickly get their products to market.

Across the electronics industry, serial bus standards for multiple purposes have been developed to address the needs of their markets and customers. A key objective of these standards is to enable interoperability with architectures across a wide range of products offered by a host of vendors.

Each specification defines attributes that products must comply with to meet the standard’s requirements. The specification defines electrical and mechanical parameters that need to be fulfilled. Interconnects need to not only comply with time and voltage requirements in the time domain, but also to losses in the frequency domain. The governing body issues standardized tests that products must pass in order to comply with the standard.

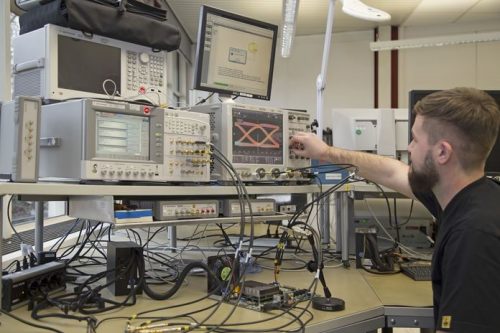

Having access to compliance measurements is required for the designer of cutting-edge solutions. They help to address potential design issues early in the design cycle and give confidence in design margins relative to the required specifications. With each new standard, comes a set of new requirements. Historically a design was commonly verified by doing transmitter compliance tests under the assumption that the receiver signal path would show a similar behavior. For new interfaces, the specification explicitly asks for receiver tests as well. While transmit signal quality is a simple and straight forward process, the receiver tests require different hardware and new test concepts. In order to ensure full compatibility and to provide the best quality, congatec invested in hardware and software that performs receiver testing.

congatec cooperates with EKH – EyeKnowHow as fast and flexible partner

Detailed know-how is required for a perfect implementation of “high speed serial interfaces”. Each design is a new challenge because of higher speeds or different topologies to implement. Although following a design guide is good, it is not always possible. Sometimes it is difficult to judge where you can deviate from a design guide without generating functional issues in your design. Other times, you have to violate the design guide to be able to implement the design at all. In this case, you might want to gain back the lost margin in other areas of your design. And of course, if you have enough margins and know them, you can reduce cost/power or improve performance of your system with an optimized design implementation.

“EyeKnowHow” is a fast and flexible partner for congatec providing the know-how, simulation, and measurement resources as required.

congatec offers their know-how and equipment to customers

With the latest big investment in compliance measurements/testing, congatec offers its customers the ability to qualify their designs to meet the standard requirements of the following high-speed serial busses:

| Interface | Supported Standard |

| SATA | Tx/Rx up to Gen.3 |

| PCIe | Tx/Rx up to Gen.3 | Gen4 TX (RX in preparation) |

| Ethernet | 10 / 100 / 1000 / 2.5G NBase-T / 10GBase-T |

| USB | 2.0 Tx, 3.1 Gen 1&2 Tx/Rx, 4.0 (in preparation) |

| DP | 1.2b / 1.4 / 1.4a |

| eDP | 1.3 / 1.4 / 1.4b |

| HDMI | 1.4 / 2.0 |

| SFI/SFP+ | |

| Memory | DDR2 (+LP), DDR3 (+LP), DDR4 (+LP) |