Description

By interleaving Renesas’ low power, high sample rate ADCs, it is possible to achieve a combination of ultra-high sample rate and very high dynamic range that is not available in today’s stand-alone ADCs.

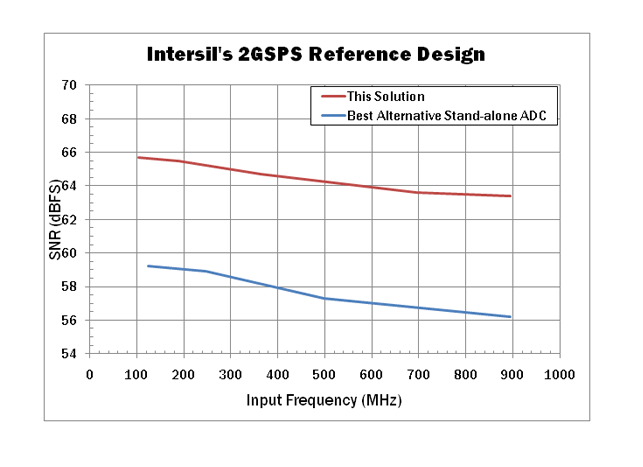

This reference design demonstrates the performance attainable by combining Renesas’ ADC technology and SP Devices interleaving algorithms. In this design, 4 ISLA112P50 12-bit, 500 MSPS analog-to-digital converters are interleaved to sample at a rate of 2.0 GSPS. At this sampling rate, the reference design provides over 6dB more SNR and 13dB better SFDR than the best alternative stand-alone ADC.

Key Features:

- Collaboration of Renesas and SP Devices

- Demonstrates 4-way Interleaving of Renesas 500MSPS ISLA112P50s

- Sample Rate: 2.0 GSPS

- Resolution: 12 Bits

- Interleave Correction Details

- SP Devices’s ADX4 provides real-time, digital, FPGA based digital interleave correction of four ISLA112P50s Performance

- Performance

- SNR = 65.5 dBfs @ Fin = 190MHz, a 6dB improvement over current best standalone 2GSPS ADCs

- SFDR = 82 dBc @ Fin = 190MHz, a 13dB SFDR improvement over current best standalone 2GSPS ADCS

Applications:

- Radar and Electronic/Signal Intelligence

- Broadband Communications

- High-Performance Data Acquisition

Courtesy: www.renesas.com