SiFive’s Arduino ready “HiFive1” dev kit features its 320MHz FE310, the first MCU using the open RISC-V ISA. Also, Samsung is rumored to be using RISC-V.

In July, San Francisco-based startup SiFive unveiled the first system-on-chips based on the open source RISC-V processor architecture: a Linux-ready octa-core Freedom U500 and a FreeRTOS-based Freedom E300. Now, the company has gone to Crowd Supply to sell an open source, Arduino compatible HiFive1 development board based on the FE300 that it claims is the fastest Arduino compatible in the world, 10 times faster even than Intel’s Arduino 101.

HiFive1

The HiFive1 is aimed at developers who want to learn more about RISC-V and start prototyping IoT and wearable devices. Blowing past the $1 Crowd Supply funding goal was no problem, and the HiFive1 campaign rolls on through Dec. 29, with packages shipping Dec. 20 ($79) or Feb. 10 ($59).

SiFive isn’t the only company prepping chips built around the completely open source RISC-V architecture. RISC-V projects are popping up in universities, startups, and semiconductor R&D labs around the world. In fact, only last week, an academic project out of Bucaramanga, Colombia called Onchip launched its own RISC-V based MCU and dev kit on Crowd Supply called Open-V. Also, Samsung is now rumored to be developing an MCU based on RISC-V. (See farther below for more on the Open-V, Samsung’s plans, and other RISC-V projects.)

We’re focusing here primarily on the HiFive1 because it’s already funded and ships in a matter of months rather than April 2018 for the Open-V. In addition, the Sutter Hill Ventures funded SiFive was founded by RISC-V inventors including Yunsup Lee, Andrew Waterman, and Krste Asanovic. RISC inventor and RISC-V backer David Patterson of the University of California is a technical advisor.

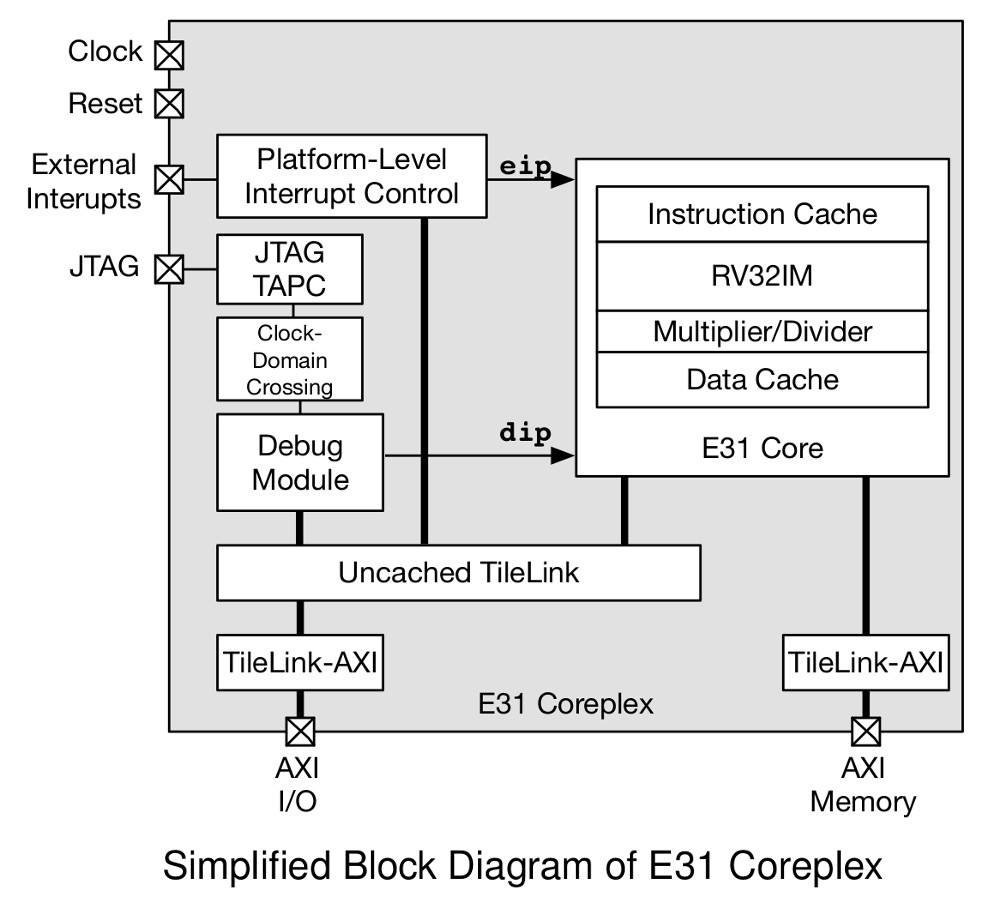

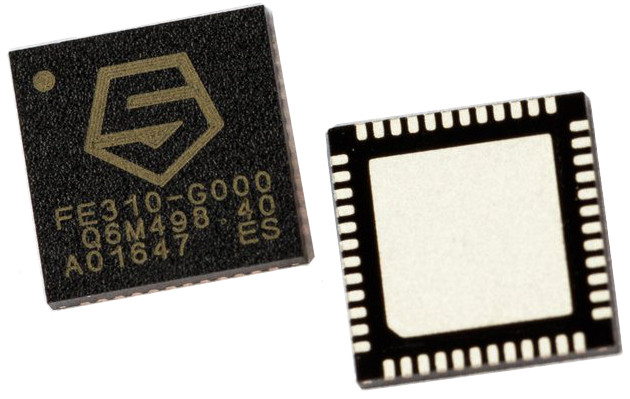

Billed as “among the fastest microcontrollers in the market,” the open source, GitHub supported Freedom E310 (FE310) SoC is built around SiFive’s RISC-V architecture E31 CPU Coreplex, a 32-bit RV32IMAC core clocked to 320MHz with 1.61 DMIPs/MHz performance. This first member of HiFive’s Freedom Everywhere line of processors is fabricated with a 180nm process by TSMC.

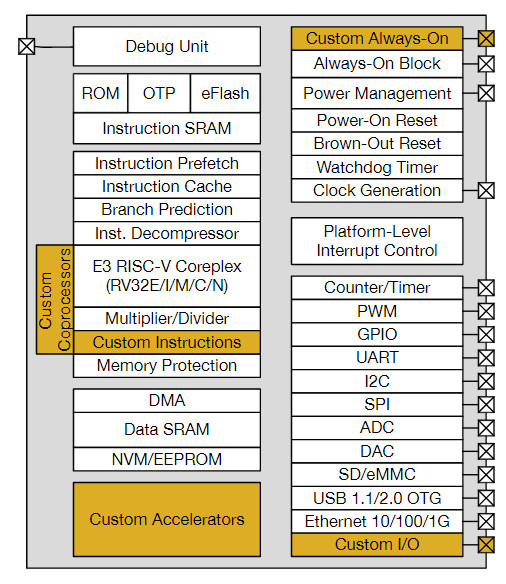

Block diagrams: E3 Coreplex and Freedom E300 SoC

The FE310 SoC is further equipped with 16KB L1, a 16KB Data SRAM scratchpad, and “hardware multiply/divide.” There’s also a debug module, “flexible clock generation with on-chip oscillators and PLLs,” and I/O support including UARTs, QSPI, PWMs, and timers.

SiFive is also selling the FE310 outright, letting customers download their own RTL (Register Transfer Logic) onto the chips. However, the company is primarily building a “chips-as-a-service” customization business.

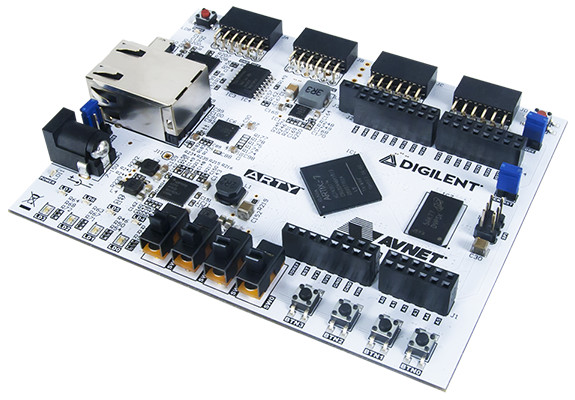

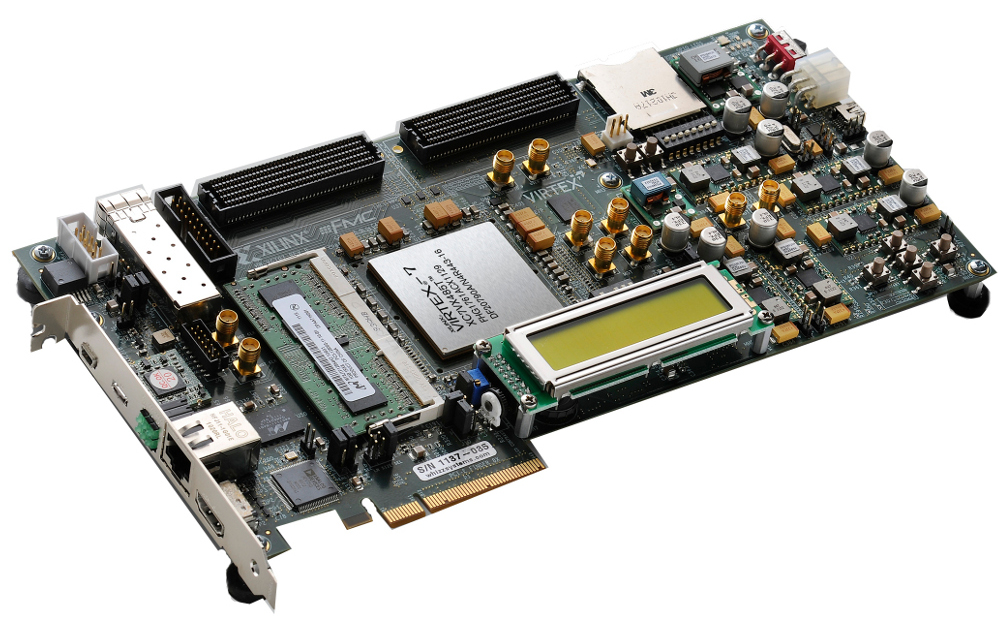

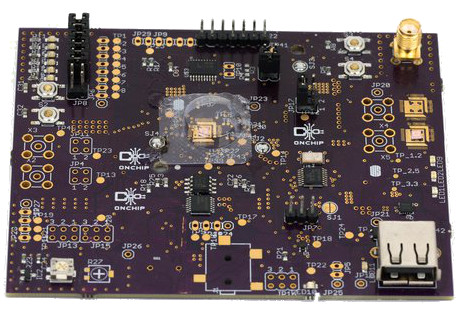

Digilent Arty (left) and Xilinx VC707

Customers can prototype for the FE310 using the HiFive1 or Digilent’s already available Arty Board featuring a Xilinx Artix-7 FPGA and MicroBlaze Soft Processing System. The $99 Arty Board also works with the Linux-driven, octa-core Freedom U500 SoC, which is also available with a high-end Xilinx VC707 board featuring a Virtex-7 FPGA. Back in July, SiFive announced Arrow’s SF2+ and EmCraft’s M2S060 boards as prototyping platforms for the Freedom E300 based on Microsemi’s Cortex-M3-based SmartFusion2 SoC FPGA, but these seem to have fallen by the wayside.

After prototyping with the HiFive1 or Arty boards, customers can then work with SiFive to build a custom RTL for the FE310. “We can make and deliver your own custom chips based on the FE310 for much less than you’d probably pay just to license a different CPU core,” says SiFive on the Crowd Supply page.

Inside the HiFive1

Aside from its fast MCU, the HiFive1 is a fairly standard Arduino compatible. The 68 x 51mm board features 128Mbit off-chip SPI flash, 19x digital I/O pins, 9x PWM pins, an SPI controller, and 3x hardware CS pins.

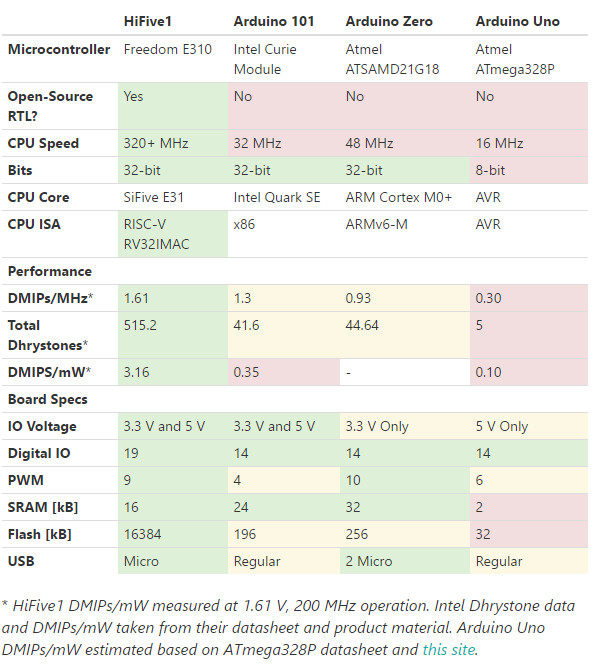

SiFive’s comparison chart between HiFive1 and other Arduino boards (left) and SiFive’s FU310 chip

The HiFive1 is further equipped with a wakeup pin and 19x interrupt pins. A micro-USB port can be used for programming, debug, and serial communications, in addition to providing 5V power. The board can also draw power from a 7-12 DC input jack. It operates at 3.3V and 1.8V, with I/O voltages listed as 3.3V or 5V. Its 3.16 DMIPS/mW rating is said to be more efficient than other Arduino boards.

The HiFive1 can be programmed with the Arduino IDE, and also ships with an open source Freedom E SDK. The SDK supports FreeRTOS, and the Freedom E SDK page on GitHub mentions IDE support for Ubuntu.

SiFive made no mention of whether a hacker board was in the making for the Linux-driven Freedom U500. The FU500 can integrate up to eight 64-bit, cache coherent “U5 Coreplex” RISC-V cores clockable today to 1.6GHz, and perhaps higher in the future. The 28nm fabricated U5 Coreplex supports the 64-bit RV64GC RISC-V architecture, and is aimed at machine learning, storage, and networking applications. (For more on the FU500 and FU300, see our previous SiFive coverage.)

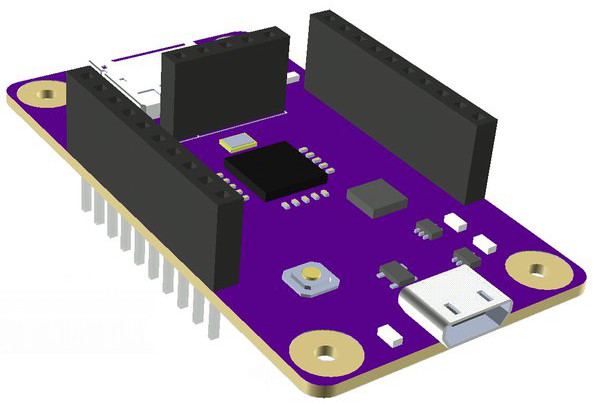

Onchip’s Open-V and lowRISC

Last week, an Onchip project from students at the Universidad Industrial de Santander in Bucaramanga, Colombia, launched its own RISC-V based Crowd Supply campaign called Open-V. The campaign, which has earned only $20,000 of its $480,000 goal, with funding ending Jan. 6, is offering a $99, Arduino compatible development board to showcase its open source, ARM M0-based Open-V MCU. One reason for the slow uptake may be that the board won’t ship until April 30, 2018, some 17 months from now.

The 130nm-fabricated Open-V chip clocks to 160MHz and offers 8KB SRAM, dual PLLs, 16x GPIO, and a pair each of ADC and DAC channels. The MCU also offers timer, SD support, a debug module and support for SPI, I2C, and UART peripherals.

Open-V development board prototype (left) and 3D render

The 55 x 30mm Open-V development board features 32KB EEPROM, micro-USB and micro-SD connections, as well as a JTAG connector and breakout header pins. 1.2 V and 3.3 V voltage regulators are also onboard.

The 64-bit RISC-V architecture was unveiled at the University of California, Berkeley over five years ago, and has been further developed since then. RISC-V is pitched as an alternative to proprietary architectures like Intel x86, ARM, PowerPC, and MIPS. RISC-V builds upon two earlier open source RISC ISAs — SPARC and OpenRISC — and seems to have largely eclipsed both efforts.

With its fully open ISA, RISC-V should encourage more free-market competition and innovation, faster time to market, and more affordable processors, say its backers. Aside from being open source, one of the main benefits of RISC-V is that it is fully modern, purpose built, and unburdened with legacy code. The potential downside for such a customizable architecture is fragmentation and incomplete compatibility.

Two years ago, a University of Cambridge spinoff called lowRISC announced plans to develop a Linux-based SoC and development board based on the RISC-V ISA. The lowRISC website now says it will “tape out our first volume chip this year.”

RISC-V Platinum members include SiFive, Draper, Google, Hewlett Packard Enterprise, IBM, Microsemi, Oracle, Microsoft, Nvidia, and Qualcomm, among others. Gold members include AMD, Espressif, Intrinsix, among others, and Silver members include ETH Zurich, Gray Research, Lattice, MIT CSAIL, and many others, including lowRISC.

Samsung tests RISC-V waters

A week ago, Korea’s ETNews published a rumor that Samsung, which is not yet listed as a RISC-V member, is developing its own MCU based on the architecture. Designed primarily for low-end wearables such as bio-patches, the chip will roughly mimic a Cortex-M0. Sources told ETNews that the processor will ship in 2017.

Samsung sold its 4- and 8-bit MCU businesses to IXYS in 2013, says the story. Now that it prepares to re-enter the market, the company perhaps determined that the tight margins in such a business could be expanded by not paying licensing fees to ARM.

Additionally, Nvidia and Qualcomm are using RISC-V to “manufacture memory controller for GPU (Graphic Processor Unit) and light processors for IoT respectively with their own independent technologies,” says the story. Both chipmakers have reverse engineered ARM designs over the years, although they also pay licensing fees to ARM for many other SoCs. If RISC-V meets expectations, three of the major ARM-based chipmakers may well decide they can live without ARM in microcontrollers. If they also eventually adopt the 64-bit RISC-V designs that run Linux, Softbank may find it paid too much for ARM.

In another sign that SoCs may have an open source future, The Next Thing recently released its open spec $6 SiP version of the Allwinner R8 SoC called the GR8. The SoC, which drives the Chip SBC and new Chip Pro COM with the help of Debian Linux-based GadgetOS, can be bought by anybody with full documentation and source code. The one major gap here is the rather opaque Mali-400 GPU. RISC-V gets around this challenge in part because the first designs, including the high-end FU500, do not include graphics.

Further information

The HiFive1 dev kit is available on Crowd Supply through Dec. 29, with packages shipping Dec. 20 ($79) or Feb. 10 ($59). More information may be found at the HiFive1 Crowd Supply page and SiFive website.

More information on Onchip’s Open-V chip and $99 dev kit may be found at the Onchip Open-V Crowd Supply page.