System engineers designing high-power applications such as electric vehicles, industrial drives and pumps, and uninterruptible power supplies are choosing Silicon Carbide (SiC) MOSFETs because of the improved efficiency and increased power density SiC technology provides over IGBTs. To maintain overall system efficiency and reduce power loss, it’s essential to pair the right SiC gate driver alongside these MOSFETS.

This blog explains the importance of system power efficiency and provides a brief tutorial on the criteria you must consider when selecting a SiC gate driver, including SiC power dissipation, SiC turn-on and off fundamentals, and how to reduce switching losses. We also introduce the NCP(V)51752, a first-of-its-kind 3.75 kV gate driver with integrated negative bias.

Every Milli-Percent Matters

When it comes to managing power loss, for high-power applications ranging from 10s of kW to megawatts, every milli-percent of efficiency matter. For example, a 100 W application running at 95% efficiency leaves only 5 W of power dissipation to be managed by your cooling strategy. In short, you could add a heatsink, and maybe a fan, and you’re good to go. But a 350-kW application running at the same efficiency yields 17.5 kW of power dissipation, requiring significant engineering and cost for managing your cooling strategy, not to mention your carbon footprint.

Reducing Power Losses

The total power loss exhibited by SiC is essentially the sum of the conduction losses plus the switching losses. SiC conduction losses are dominated by I2R, where I is the drain current (ID) and R is the RSDON or the resistance of the Drain to Source current path when the SiC MOSFET is fully turned on. System engineers can design for very low conduction losses by choosing low RDSON SiC MOSFETs, configuring multiple SiC MOSFETs in parallel, or both.

SiC switching losses are more complicated, influenced by parameters like the Total Gate Charge (QG(TOT)), the Reverse Recovery Charge (QRR), Input Capacitance (CISS), Gate Resistance (RG), EON losses and EOFF losses, to name a few.

QG(TOT), Total Gate Charge

The Total Gate Charge QG(TOT) is the amount of charge (Coulombs) that the gate driver needs to inject into the gate electrode to turn the MOSFET fully on or off. Typically, the QG(TOT) is inversely proportionate to the RDSON. So, as system engineers select lower RDSON SiC MOSFETs to reduce conduction losses in their high-power applications, the gate drive source (turn on) and sink (turn off) current requirements increase proportionally.

System design for lower switching losses becomes quite challenging because, on one hand, you want to turn on and off as quickly as possible to minimize switching losses. But on the other hand, faster switching speeds can introduce unwanted electromagnetic interference (EMI), as well as potentially dangerous and unintended parasitic turn-on during intended switch turn-off, especially in half-bridge topologies.

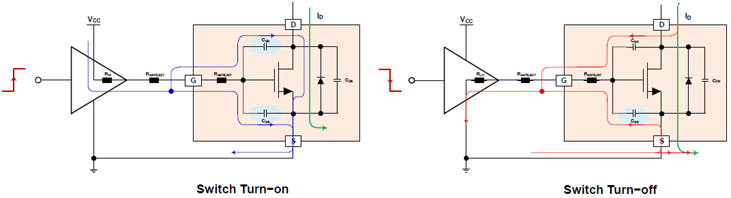

Turn-On and Turn-Off

To operate a MOSFET and start conduction, a voltage must be applied to the gate terminal that is relative to the source terminal. Dedicated drivers are used to apply voltage and provide drive current to the gate of the power device. The gate driver serves to turn the power device on and off by sourcing or sinking the drive current, respectively. In order to do so, the gate driver charges the gate of the power device up to its final turn−on voltage, VGS(ON), or the drive circuit discharges the gate down to its final turn−off voltage, VGS(OFF). The transition between the two gate voltage levels requires a certain amount of power to be dissipated in the loop between the gate driver, gate resistor, and power device.

Today, high−frequency converters for low- and medium-power applications are predominantly making use of power MOSFETs. However, gate drivers are not only for MOSFETs, but they are also ideally suitable for relatively new and esoteric devices from the wide band gap group such as SiC MOSFETs and GaN (gallium nitride) MOSFETs. Where higher driving current is required for fast ON/OFF power switching, the best-performing devices in use today are usually SiC MOSFETs.

Parasitic Turn On

Because of the very high di/dt, excessive ringing can occur when the gate driver reaches the minimum Gate to Source Voltage. This is compounded by parasitic capacitances and inductances augmented by PCB layout and packaging, causing inductive kicks during turn off. These inductive kicks can inadvertently trip the VGS(TH) causing an accidental turn on during intended turn off, which can trigger disastrous results. For example, consider a half bridge application. When the low side switch is turned off and the high side switch is about to be turned on, low side switch can be accidently turned on (VGS(TH) tripped by inductive kick), causing both the high side and low side switches to be simultaneously turned on (shoot-through current). This may result in a direct short from the high voltage rail to ground, which can cause damage to the MOSFET. One very effective mitigation against this issue is to swing below 0V, down to -3V or even -5V during turn off, creating some headroom or margin against this accidental inductive kick tripping the VGS(TH).

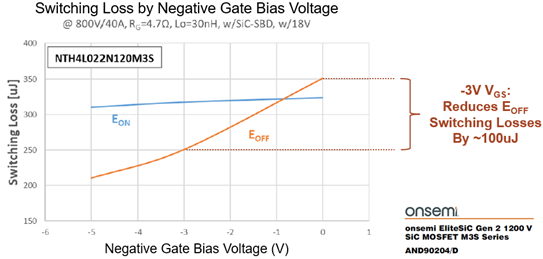

Switching Losses

The plot in Figure 2 (source: AND90204/D), where the x-axis captures the Negative Bias Turn off voltage from 0V to -5V, and the y-axis captures switching losses (µJ), illustrates the second advantage for negative bias turn off resulting in reduced EOFF switching losses. In fact, by lowering the turn off voltage from 0V to -3V when driving onsemi’s Gen 2 “M3S” series of SiC MOSFETS designed specifically for high switching frequency applications, switching losses can be reduced by as much as 100 uJ. An EOFF reduction from 350 µJ at 0V to 250 µJ at -3V negative bias turn-off yields 25% reduction in EOFF losses. And remember, every milli-percent matters!

Gate Drive Turn Off with Integrated Negative Bias

onsemi offers many high voltage, high power isolated SiC gate drivers that support “external negative bias” during turn-off, where the system supplies the -3V or -5V to the gate driver to generate the negative swing.

The NCP(V)51752 is a new family of isolated SiC gate drivers featuring internal negative bias.

This feature saves system costs because the system does not have to supply the negative bias rail to the gate driver – the NCP(V)51752 does it on its own.

The four below trim options of the NCP(V)51752 are available. Other options are available on demand.

- NCP51752CDDR2G: Industrial, UVLO: 12V, Negative Bias: -5V

- NCP51752DBDR2G: Industrial, UVLO: 17V, Negative Bias: -3V

- NCV51752CDDR2G: Automotive, UVLO: 12V, Negative Bias: -5V

- NCV51752CBDR2G: Automotive, UVLO: 12V, Negative Bias: -3V

Conclusion

The NCP(V)51752, 3.75kV, 4.5A/9A, Galvanic Isolated (input to output), Single Channel SiC Gate Driver with integrated negative bias:

- Mitigates against accidental turn-on during intended turn-off.

- Reduces EOFF switching losses by 25%.

- Saves system costs.