As semiconductor scaling approaches fundamental limits, the industry is increasingly adopting chiplet-based architectures and heterogeneous integration to drive performance, power efficiency, and functionality. This shift is enabling new computing paradigms, from high-performance computing (HPC) to artificial intelligence (AI) accelerators and edge devices. This article explores the latest developments in chiplets, their role in modern semiconductor design, the challenges that lie ahead, and the technical innovations driving this revolution.

The Rise of Chiplet-Based Architectures

Traditional monolithic chip designs are facing bottlenecks due to escalating fabrication costs, yield issues, and power constraints. Chiplets offer a modular approach, enabling manufacturers to:

- Improve Yield: Smaller dies reduce defect density, improving overall yield and lowering per-unit cost.

- Enhance Performance: Optimized chiplets for different functions allow greater efficiency and performance scaling.

- Reduce Costs: Advanced nodes can be selectively used for performance-critical chiplets while other functions remain on mature nodes to balance cost and efficiency.

- Enable Scalability: Chiplets allow seamless integration of different process nodes and functionalities, ensuring adaptability across multiple applications.

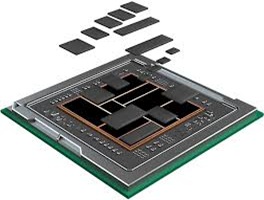

The flexibility of chiplet-based designs is enabling complex computing architectures, where compute, memory, interconnect, and I/O functionalities are independently designed and integrated into a heterogeneous multi-die system.

Heterogeneous Integration: The Next Evolution in Semiconductor Design

Heterogeneous integration refers to the assembly of multiple dissimilar semiconductor components into a single package. This includes logic, memory, power management, RF, photonics, and sensors, combined to optimize system performance.

Key benefits of heterogeneous integration:

- Increased Performance Density – More transistors can be packed per unit area without the constraints of monolithic die sizes.

- Energy Efficiency – Improved power management through advanced interconnect technologies and proximity of critical functions.

- Customizable Architectures – Modular design allows for application-specific optimizations in AI, HPC, and embedded systems.

- Multi-Node Manufacturing – Different components can be fabricated using different technology nodes, enabling cost and performance trade-offs.

Key Technologies Enabling Chiplets and Heterogeneous Integration

- Advanced Packaging Technologies

The success of chiplet integration depends on sophisticated packaging methodologies that ensure low-latency, high-bandwidth interconnects while maintaining power efficiency. The latest packaging technologies include:

- 2.5D Integration: Uses an interposer (silicon or organic) to connect multiple chiplets, offering high-speed interconnects with reduced power consumption.

- 3D Stacking: Enables vertical stacking of dies using Through-Silicon Vias (TSVs), achieving high interconnect density and bandwidth.

- Fan-Out Wafer-Level Packaging (FOWLP): Enhances signal integrity by reducing interconnect length and improving thermal performance.

- Wafer-to-Wafer and Die-to-Wafer Bonding: Enables ultra-dense 3D integration for logic-memory co-packaging and AI processors.

- High-Speed Interconnects and Chiplet Standards

Efficient interconnects are critical for seamless communication between chiplets. Recent advancements include:

- Universal Chiplet Interconnect Express (UCIe) – An industry-standard interface for connecting chiplets from different vendors with minimized latency.

- Advanced Interface Bus (AIB) – Developed by Intel, enabling high-bandwidth chiplet communication for FPGA and AI accelerators.

- Bunch of Wires (BoW) – A low-power interconnect standard optimized for edge computing and AI applications.

- Silicon Photonics Interconnects – Optical interconnects enable ultra-high-speed data transfer between chiplets in HPC environments.

- Power Delivery and Thermal Management

As chiplet architectures increase integration density, power and thermal constraints become critical challenges:

- Advanced Power Distribution Networks (PDNs) optimize efficiency across chiplets, ensuring stable voltage regulation.

- Thermal Interface Materials (TIMs) and liquid cooling solutions mitigate heat buildup in densely packed chiplet systems.

- On-Package Voltage Regulation (OPVR) reduces power loss in multi-die systems and enhances dynamic power allocation.

Industry Adoption and Notable Implementations

AMD’s Chiplet Approach

AMD pioneered the chiplet strategy with its Zen architecture, integrating multiple CCD (Core Complex Dies) with an IOD (I/O Die). The approach enhances yield and scalability while maintaining high performance.

Intel’s Heterogeneous Integration with Foveros

Intel’s Foveros 3D packaging allows high-performance logic stacking, demonstrated in products like the Meteor Lake processors, which integrate high-performance and power-efficient cores within a single package.

TSMC’s CoWoS and SoIC

TSMC’s Chip-on-Wafer-on-Substrate (CoWoS) and System on Integrated Chips (SoIC) technologies provide cutting-edge 2.5D and 3D integration solutions for AI accelerators and HPC applications.

NVIDIA’s Hopper Architecture

NVIDIA’s Hopper GPU integrates multiple HBM stacks and logic dies using TSMC’s CoWoS-S technology, demonstrating the potential of chiplet-based HPC solutions.

Challenges in Chiplet and Heterogeneous Integration

Despite the benefits, challenges remain:

- Interconnect Latency and Bandwidth – Efficient, low-latency interconnect solutions are required for high-speed data exchange between chiplets.

- Standardization Issues – Lack of universal standards complicates cross-vendor chiplet integration and interoperability.

- Design Complexity – Optimizing power, thermal efficiency, and routing in multi-die architectures requires advanced EDA (Electronic Design Automation) tools.

- Manufacturing Costs – While chiplets can reduce per-unit costs, the added complexity in packaging and interconnects can offset savings.

- Security and Reliability – Multi-vendor chiplet integration introduces security risks and potential failure points that require robust testing methodologies.

The Future of Chiplets and Heterogeneous Integration

The industry is rapidly evolving towards fully modular semiconductor designs, driven by:

- AI and Machine Learning – Custom chiplets optimized for AI workloads are expected to dominate future architectures.

- 3D Heterogeneous Computing – Next-generation chips will feature tightly integrated compute and memory stacks for high-speed processing.

- Chiplet Ecosystem Growth – Collaboration among semiconductor giants is leading to open standards like UCIe for universal chiplet interoperability.

- Quantum and Neuromorphic Computing – Emerging computing paradigms are leveraging chiplets for specialized, high-performance computation.

- AI-Assisted Chiplet Design – Machine learning and AI-driven automation are revolutionizing semiconductor design, optimizing layouts for power and performance efficiency.

Conclusion

Chiplets and heterogeneous integration represent the next frontier in semiconductor design, overcoming the limitations of traditional monolithic scaling. With industry leaders like AMD, Intel, TSMC, and NVIDIA driving advancements, we are entering an era of unprecedented performance and efficiency in computing architectures. While challenges remain in standardization, interconnects, and thermal management, continued innovation promises a future where chiplets become the fundamental building blocks of next-generation processors, ushering in a new era of modular, high-performance computing.